ISSN(O): 2320-9801

ISSN(P): 2320-9798

# International Journal of Innovative Research in Computer and Communication Engineering

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

**Impact Factor: 8.771**

Volume 13, Issue 8, August 2025

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

## The Evolving Landscape of Hardware and Firmware Engineering in Cloud Infrastructure

#### Srikant Sudha Panda

Senior Technical PM, Microsoft, USA

ABSTRACT: This study presents the idea of integrating hardware and firmware engineering in the context of company cloud-based architectures to support performance, stability, and security for workloads involving AI, big data, and edge computing. The research points to co-development being essential through the presentation of co-developing techniques, illustrated by some examples, including Microsoft Azure Cobalt 100 CPU and Heritage Maia 100 AI Accelerator. The study contends that techniques involved in co-development lifecycles would support improving validation time and redundancy through automated regression testing, virtualized simulations, and agile processes. The co-development methodology involves hardware engineers, firmware developers, software architects, and cloud operators working effectively together as integrated teams to identify and fix both scaling issues and integrated aspects. There is mention of trends that respond to security and reliability challenges that are commonplace in large cloud data centers, including AI-based automated testing, validation-based digital twin, and continuous, regular firmware updates. Most importantly, the research highlights \_co-developing\_ firmware stacks for mixed heterogeneous computing (accelerators) engaged with DevOps management lifecycle as a clear goal. Ultimately, this research affirms that an integrated partnership of hardware/firmware is required to deliver available, reliable, scalable, and, importantly, secure cloud services to improve customer experience while taking advantage of the rapid nature of digital business transformation in the cloud.

**KEYWORDS:** AI, Big Data, Edge Computing, Automated Regression Testing, Virtualized Simulations, Agile Methodologies, DevOps-driven Lifecycle

#### I. INTRODUCTION

Hardware engineering involves the design, development, testing, and management of physical elements of the computer systems and electronic devices relating to cloud environments under hardware's entire lifecycle. In this sense, hardware engineering will be concerned about reliability performance, and scaling in a data center. Firmware engineering is mainly concerned with low-level software that provides a bridge to hardware, boots a device or communicates between higher-level software and the hardware. Embedded software is critical in controlling and optimizing a device such as a solid-state drive (SSD) or artificial intelligence (AI) accelerator. Both hardware and firmware engineering are key areas for developers to create robust and high-performance cloud infrastructures with good physical technology integration with software controls.

Hardware and firmware engineers are instrumental to the cloud infrastructure, data center, and application space of AI accelerators, ensuring the physical hardware and the embedded software work as intended, providing reliability, efficiency, and performance. In cloud computing, hardware engineers design the core components, such as the servers and storage devices, while firmware engineers utilize software optimizations in their firmware to promote uptime and reliability, with low-level fast-development enhancements for fault tolerance or potentially seamless debugging. Both hardware and firmware engineering teams work closely together in improving overall performance, enhancing the ability to add new server data workloads, and moving towards energy efficiency, as cloud providers do provide extensive cloud workloads. Similarly, but specifically for AI accelerators in history, hardware developers engineer specialized processors that improve computational power and utilization for AI tasks, while firmware engineers create low-level control software for processor controls and optimization. These accelerators follow due process tests before deploy to pass the performance, security, and rich service durability practices created to test continuously throughout the industry prior to deployment [1].

To ensure effective validation, deployment, and optimization of complex systems in data centers or cloud facilities, strong collaboration between the firmware and hardware teams is essential. Validation requires fully integrated

DOI:10.15680/IJIRCCE.2025.1308061

www.ijircce.com

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

validation to allow the hardware and firmware to be tested together to identify integration issues as early as possible. For the bring-up process, the firmware teams provide all necessary control and diagnostics to enable the hardware teams to verify design intent and functionality, and this collaboration reduces time-to-market and expedites troubleshooting. Since the firmware manages critical components of performance and reliability (e.g., error handling and power management), working together is paramount to harnessing the full potential of the hardware while ensuring stability. Partners also enhance discovery and resolution of issues that crop up during a field deployment situation, as the issues can be dealt with collaboratively as a work team. Finally, it is important to note that collaboration is critical when applying design changes and preventing design incompatibility as hardware and firmware are both continuously evolving and being measured, particularly in larger scale cloud facilities and AI deployments [2].

The disciplines of firmware and hardware engineering are deeply intertwined because firmware is the software programming that runs on hardware. Their close relationship allows firmware to work closely with hardware, taking software commands and turning them into electrical signals needed for the performance of the hardware. The presence of some level of firmware, especially in chips like SoCs and CPUs, improves the hardware and, therefore, the intended functionality of the component, allowing the components to operate dynamically and instantaneously, worth close communication with systems' software. The unique relationship between firmware and hardware provides a specific set of advantages, such as performance and reliability for the whole system, as firmware is specifically designed to utilize the hardware, thus minimizing faults and maximizing performance. Firmware and hardware interrelationship also speeds up development and testing cycles since design validation and simulation can occur earlier in the design process, which reduces time-to-market and prototyping costs. Maintenance and troubleshooting of hardware systems also benefit from the interrelationship of firmware and hardware because problems spanning across the hardware and software components of a system can be identified more quickly. There is also improved version control and communication between firmware and hardware, mitigating risk in the event of mismatched firmware and hardware versions. Firmware and hardware interrelationship makes upgrading firmware much easier and increases the longevity and scalability of a product, since devices can now take advantage of new capabilities without incurring the cost of developing a new device [3].

The majority of hardware and firmware integration architectures evolve around binding hardware components to the embedded software in charge of orchestrating them. This gives the appearance of seamless operation and interaction. Hardware and software integration strategies include the use of firmware and device drivers, both of which mediate the operations of higher levels of software from hardware. Firmware is responsible for supporting hardware aside from the initialization of the hardware when powering on the system and carrying out real-time operations, while the device driver translates commands from software into a format the hardware is able to interpret. The firmware and hardware communicate with one another through standardized protocols that specify the data exchange format and electrical signaling for the specific task of reading sensors or controlling actuators. Examples of such protocols are SPI, I2C, UART, and CAN bus. The physical memory architecture is also a significant component of firmware and hardware integrations. Firmware must reside in some form of memory, whether it is in an external FLASH chip or built-in ROM/EEPROM. The context of where the firmware is stored will influence updates and functionality.

A modular layered firmware design architecture breaks the concerns into distinct bootloader, device drivers, middleware, and application layers, facilitating greater scalability and maintenance through independent development and testing of each of the layers. Integration testing architectures support testing of hardware components individually through embedded utilities or simulated environments, while maintaining the assurance that the required hardware features are functioning as expected (further firmware management). System level methodologies include methods of performing point-to-point integration for simple connections, centralized methodologies (hub-and-spoke) for connections to a ground pane, and enterprise service bus (ESB) architectures for standardized communication connections for complex designs (particularly in "cloud integration" designs) [4].

Several key factors are validating digital signatures to ensure the updates are executed with both authenticity and integrity, as the digital signature allows verification before installation, in order to ensure that there's no unwanted alteration. Secure communication channels, like TLS, are also important to send updates without eavesdropping or a boy-in-the-middle attack. Access and authorization must also be controlled, along with the implementation of privileges to adjust firmware, which would lower the possibility of malicious firmware being inadvertently released without authorization. Where possible, rollback protection needs to be implemented to disallow downgrading to previous versions which could be exploited, while allowing for upgrades to the most current versions of firmware.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

Threats do evolve and will continue to do so, so constant monitoring and adjustments will be necessary. Quickly patching or sustaining the security posture should be established. For this reason, firmware should be developement to integrate across multiple environments with the best defenses against memory safety issues, or buffer overflow attacks, to prevent threats from executing code injections. Lastly consistency and standards-based framework updates will increase security as this removes differences from devices, creating less variation for threats and incidents. [5].

The document discusses various models of threats that involve attacks on firmware updates. These threat models are unauthorized firmware modification, in which attackers modify the update package to execute arbitrary code; rollback or replay attacks that exploit old firmware to discover vulnerabilities; tampering with firmware updates in transit (referred to as Man-in-the-Middle attack, or MitM, which occurs over insecure communication connections); unauthorized updates that contain malware and overwrite or sideload firmware using weak processes of authentication; supply chain attacks from compromised firmware during manufacturing or after distribution; physical attacks that enable an attacker to change firmware via memory access or a debug port; malicious firmware payloads that allow for lateral movement inside a network of systems or to exfiltrate data; and violations of trusted execution where unauthorized firmware is installed at boot time that undermines integrity. Finally, flaws in the firmware update protocols or processes can be manipulated by an attacker to obtain control of the device, due to zero-day vulnerabilities, poor code, a lack of validation, and/or a lack of encryption on the update. [6].

#### II. SYSTEM OVERVIEW

Management of the hardware lifecycle incorporates the totality of the life of a hardware asset, through design and eventual retirement, in such a way as to maximize performance, reliability, and life. The first phase is design, which is the phase where all specifications on the hardware is stratified in addition to the technical and business requirements for the hardware are factored in relative to the fitting component design, architecture, and interoperability with other systems. The second phase is the qualification phase where the prototypes are thoroughly tested and measured against standards and readiness for production. The third phase is the examination phase, which includes personal observations as well as stress tests and performance tests ascertaining the integration of hardware and software to issue a preproduction release. The fourth phase is the long-term engineering phase, which handles the long-term aspects of the asset after it has been deployed, mainly to address lifecycle maintenance and other post-deploy updates, assuring the hardware runs as intended and fits the evolving patterns of customers as requested while maximizing reliable operability with minimized costs and downtime [7].

The HLM (Hardware Lifecycle Management) checklists include key steps associated with both the Design Gate and the Qualification Gate. In the case of the Design Gate, the HLM checklist ensures hardware parameters (technical and commercial) are aligned, that the architecture and components will meet expectations for performance, and that the design works with existing systems. The checklist also recognizes acceptance of the design drawings, assessed price point viability, industry standards adhered to, assessed risk acceptance methodology, and documentation completeness prior to qualification testing and prototyping. For the Qualification Gate, the HLM checklist focuses on physical inspection of appropriate prototypes against design standards, progressed to thorough functional testing; and prototype stress testing against environmental parameters. In the qualification gate, the HLM checklist also establishes durability of physical hardware; test the compatibility of any firmware, institutions for safety certifications; test and assess data, validate for significance against preliminary known issues; and engage in initial limited deployment or pilot production plans. Both gates are necessary in confirming hardware readiness, robustness and durability to scale production, particularly for projects including fog or cloud infrastructure and AI hardware, lessening risk, working to improve quality, and creating opportunities for collaboration between design, test prep, and manufacturing [8].

- The systematic lifecycle of firmware development and verification for an embedded hardware controller aims to ensure a robust and performant embedded software solution that enables the desired functionality of its hardware. There are typically a number of sequenced steps involved in the process of firmware development which are needed to achieve reliable behaviour in embedded systems.

- Requirements Analysis: Identify functional and non-functional requirements based on stakeholder needs assessment and hardware capability assessment

- System Design: Design hardware interface, driver, module and interrupts with defined memory consumption and communication protocols, as well as components of embedded system

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

- Implementation: Implement firmware in languages like C or assembly considering hardware registers, temporal and resource constraints, as well as necessary middleware and device drivers to achieve proper hardware control

- Debugging and Testing: Perform testing on hardware or simulations at a system, integration and unit level in order to measure for ability to respond in real-time while being reliable and executing functional and non-functional requirements confirmed with debugging protocols

- Records: Support maintainability and troubleshooting with detailed documentation (i.e. code documentation, architecture diagrams, test cases, and user manuals).

- Implementation: Program firmware into devices using either over-the-air updates or flashing, considering version control and verification of successful installation.

- Upkeep and Support: Adapt firmware to provide ongoing bug fixes, security patches, feature improvements, and firmware updates throughout its lifecycle to keep it safe and functional.

Hardware control is ultimately based on the development of firmware/control to enable a device to perform specific tasks with optimizations in effectiveness, efficiency, etc. It is necessary to achieve thorough validation of the firmware functionality in complex hardware systems (especially in complex ecosystems such as cloud infrastructure and AI accelerators), while ensuring reliability and effectiveness beyond interaction and environmental constraints.

Quality control and automation are key practices to ensure that hardware platforms/embedded systems are reliable, functional, and dependable when testing firmware and hardware. Test planning, along with testing of hardware and firmware components, must be done to encompass unit, integration, system, and regression testing, and all tests must be aligned with all hardware and firmware specifications. Functional verification ensure that the requirements such as communication protocols and real time response are being met. Hardware-in-the-Loop (HIL) testing includes real hardware with virtual environments to enable the designer to verify design pre-deployment. Environmental and stress testing determines hardware performance under extreme conditions.

An automated pipeline within a continuous integration system involves firmware tests to enable early fault discovery and ongoing verification. The automation capability can be applied to the firmware build and deploy process within a continuous integration/deployment setup with little or no human intervention. Remote hardware tests open up even broader automated testing functionality to be performed on real hardware devices. Automated regression testing can benefit as code performance and reliability gaps are quickly discovered after code changes occur; in some cases, testing can be carried out through simulation or emulation to help mitigate the constraints of hardware testing. The advantages of this practice are improved test coverage, improved reliability, improved time to market, in addition to improved validated testing for embedded systems and reliability, and improved resource optimization with scalable test infrastructure [8].

Successful technology project validation, bring-up, and optimization relies on firmware and hardware engineers working closely together. The engineers' engagement and similar background leads to discovery of integration bugs sooner because the hardware engineer has a solid understanding of the firmware needs of the software engineer, and the firmware engineer is knowledgeable about limits of the hardware carrier and can help avoid expensive redesigns down the road. The two engineers working together also allows firmware engineers to significantly reduce the bring-up time during development and reduce overall time to market, using development boards or simulators. Doing validation together ensures all hardware is exercised in the operational context expected for reliability and reduces adverse surface interaction with hardware and firmware that could introduce functional gaps. Sharing designs or revisions and results of tests can improve traceability, change control and reduce discrepancies between versions and potentially prevent errors introduced through interoperability. Overall, collaboration between the firmware and hardware teams can bring added innovations and quality, which should positively impact better engineered, reliable solutions for the intended complexities of the environment. In short, all those working in firmware and hardware together at the same time mitigates risks, lowers costs, improves quality, and time to market for best modern high-performance technology projects [10].

Today's embedded systems and cloud systems use complex software with necessary hardware. Important hardware includes NAND flash memory, which is used in solid-state drives (SSDs). These drives offer data storage that is faster, more reliable and energy efficient than traditional hard drives. A good example of SSD technology would be the Micron 2400 NVMe SSD, which uses a PCIe Gen4 interface. NVMe takes advantage of SSD technology by creating access patterns that are extremely fast with low-latencies. Dual Inline Memory Modules (DIMMs) are also important

DOI:10.15680/IJIRCCE.2025.1308061

www.ijircce.com

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

hardware components that provide temporary storage for data. FPGAs (Field Programmable Gate Arrays) allow the ability to perform a specialized processing type related to certain system needs. SoC (System on Chip) technology allows multiple components to be on a single chip for efficiency of power and space. The hardware is managed by the Basic Input/Output System (BIOS), which initializes hardware when the system is powered on and supplies runtime services. Firmware technology is complex as it includes functions belonging to drivers, offering functionality and bootloader that initialize and verify the hardware initialization of the firmware. There is also verification firmware, that confirms the hardware is functioning to meet specific performance. Together the mixture of hardware and firmware are the physical hardware of embedded systems and cloud systems that are reliable and high-performance that will balance physical hardware with the critical software management of the devices to manage complex workloads efficiently.

In order to support meaningful validation and continued growth, the hardware and firmware test tools used are based on automation frameworks, DevOps integration, and hardware-in-the-loop (HIL) testing. Automated testing frameworks, such as the Robot Framework and Pytest, help firmware tests by offering the required objects and keyword-driven testing while improving test consistency and coverage through various automated testing scopes, including regression and unit tests. The use of emulation and simulation applications establishes a non-real or constructed hardware setting that helps facilitate early detection of issues and can help minimize costs, since firmware verification can be done without real hardware. DevOps integration permits construction, deployment, and testing of the firmware for the specific hardware with less effort during firmware testing and construction cycle through Continuous Integration/Continuous Deployment (CI/CD) pipelines. CI/CD pipelines enhance feedback cycles and often minimize risks or errors from human factors through integration of automated integration. For example, tools such as Jenkins and Azure DevOps allow automated flashing of firmware and facilitate collection of test results remotely on multiple hardware units, during the firmware test. HIL testing is a methodology that uses a combination of either a simulated system performing emulated functions/simulation with real hardware to validate firmware implementation can function under realistic execution environments prior to deploying it to full production deployment. HIL testing not only allows for testing of the firmware under more rigorous conditions, but it optimally utilizes the benefits of test automation with real hardware reliability support, therefore allowing firmware test frameworks to manage and execute automated testing [11].

#### III. INDUSTRY TRENDS AND CHALLENGES

Rapid developments in ai, machine learning and high-performance compute are causing the demand for specialized hardware and ai accelerators in cloud data centers to grow substantially. The cloud data center accelerator market is expected to see global compound annual growth of +15.9% reaching USD 124.6 billion in 2035, driven by ai acceleration technology and next-generation processors for ai workloads. Demand for accelerators is almost evenly split between ai/ml training and high-performance compute/data analytics, which has led to substantial investments in specialized artificial intelligence hardware in the form of gpus and custom asics. The ongoing evolution of gpu designs and ai-centric processors has not only led to greater demand for efficiency but has also increased demand for scalable forms of acceleration hardware. Cloud data centers are adapting their cloud architecture for high-density ai accelerator clusters from leading providers such as Google, AWS, and Meta, through increasing rack densities and cooling capacity to address higher power consumption. New government deployment initiatives and partnerships in places like South Korea and Japan are also supporting the deployment of accelerating technology in computing workloads. As the demand for AI workloads grows, data center power consumption is projected to increase 165% by 2030 and will require new power infrastructure and thermal management techniques. The increased adoption of edge AI and autonomous systems primarily drives the need for application-specific accelerators for real-time data processing capabilities [12].

The rapid growth of AI, machine learning, and high-performance computing has significantly increased the demand for specialized hardware and AI accelerators in cloud data centers. The global data center accelerator market is expected to expand with a compound annual growth rate of 15.9%, to USD 124.6 billion by 2035 because of the advancements in AI acceleration technologies and processor architectures that work on AI workloads. The demand for accelerators is evenly split between AI/ML training and high-performance computing, a trend for which we have provided a table in below Table 1, summarizing some of the public forecasts that generalizes the markets share for accelerators. Technology advancements in the design of accelerators helps to meet the demand for scalable and efficient acceleration hardware. Cloud data centers are upgrading their underlying infrastructure to manage high-density AI accelerator clusters from major AI accelerator providers, addressing power distribution and cooling systems as part of their

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

upgrades. There are geographic initiatives occurring in Korea and Japan to promote the deployment of accelerators with the assistance of government initiatives and various partnerships. However, in recent years, as the adoption of AI technologies increasingly increases; data centers are projected to consume 165% more power by the year 2030. With AI adoption, only time will tell whether more power infrastructure will be needed to accommodate this increased energy use and how it will deal with thermal management. In addition, the expansion of edge computing and autonomous systems will continue to drive demand for specialist accelerators within compatibilities with real-time processing.

| Architecture | Description               | Strengths           | Use Cases          |

|--------------|---------------------------|---------------------|--------------------|

| GPUs         | Massively parallel cores, | Flexibility, high   | AI training,       |

|              | tensor cores              | throughput          | inference          |

| NPUs         | ASICs optimized for       | Energy-efficient,   | Large-scale AI     |

|              | neural network inference  | optimized AI ops    | inference          |

| FPGAs        | Programmable logic        | Low latency,        | Real-time AI, edge |

|              | gates, customizable       | reconfigurable      | computing          |

| ASICs        | Custom AI chips for       | Highest efficiency, | Dedicated AI       |

|              | specific models           | low power           | accelerators       |

Table 1: Top Hardware Architectures for AI Accelerators in Data Centers

Managing hardware-software integration at scale in data centers presents multiple challenges. A variety of software and hardware is often provided by vendors that interoperate with complex configurations which involve careful configuration management and integration testing. New technologies are integrated with existing systems and will also include considerations for modern systems and legacy systems. This involves an activity to consider backward compatibility, migration, and planning activity. Security considerations must also account for expanded attack surface areas and considerations for the situations of misconfiguration, near real-time monitoring, and coordination of security policies to ensure unauthorized access has not occurred during test activity. When workload changes necessitate effective resource/staffing and scalability concerns, automation and AI-driven platforms are often utilized to optimize instructional updates. Data consistency and fault tolerance are two primary criteria associated with migrations and should be carefully planned with review back-up protocols to avoid overwriting data. Operational complexity can often amplify based on breadth and depth of the specialized skillsets needed for each operational mission, where multilayer corporate teams of specialized multicultural operations will be necessary. This could overstretch staff resources and necessitate ongoing development of staff skills and spaces for co-development of skills in operations. Finally, dependent on vendors may compartmentalize solutions in a modular crisis management methodology, keeping the burden of internal knowledge, and flexibility, with additional risk [13].

It is important for data centers to regularly update their firmware to secure hardware, maintain reliability, and provide maximum performance. A comprehensive plan should be created to address the balance between the risk associated with downtime and the requirements of security improvements or performance upgrades. This plan should consist of regularly scheduled updates to address vulnerabilities and an inventory tracking system to provide certification that all devices being used meet the appropriate firmware level. Centralized management for a variety of firmware throughout servers and storage, as well as networking, is recommended in your strategy. Updates should occur via secure channels to ensure that updates are not unauthorized, as well as network segmentation and request controls, to minimize the attack surface during updates. Testing of updates prior to execution, as well as executing updates progressively, will likely offer many opportunities to potentially detail issues early and reduce any impact associated with upgrades that may be faulty. Communication with your stakeholders, discussing expectations and monitoring deployment, provide opportunities to improve overall outcomes. As the complexity of systems involving hardware increases, the implementation of AI-based firmware update tools, only when a system is considered at risk, is an effective method of improving update strategies, based on priority items of your strategy. The benefits of this outline will be addressing firmware vulnerabilities, increasing the efficiency of hardware and avoiding unscheduled downtime. In summary, an improved process of reliable firmware management is important for resilience within the data center, ultimately improving security, compliance, and performance of increasing complexity found in cloud environments [14].

The introduction of DevOps and automation is reshaping the way we develop, test, and deploy embedded software. The key to this shift is embracing Continuous Integration and Continuous Delivery (CI/CD) practices for our firmware.

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

CI/CD reduces human error and shortens release cycles by automating the deployment of new firmware, including building, testing, packaging, and deploying the firmware. CI/CD relies on tooling (e.g., Git, CMake, automated testing frameworks) to generate firmware images. Dedicated toolchains for embedded devices ensure the builds are the same across various target systems. Automated testing frameworks can run tests on actual hardware as well as simulations of hardware to increase reliability. Incorporating Hardware-In-The-Loop (HIL) testing in the CI pipeline improves quality by ensuring the firmware works correctly with either true hardware or simulated models and exposes integration issues earlier in the development.

Rapid issue identification and resolution are made possible using automated feedback loops and real-time monitoring, as well as rollback or patch capabilities, which are vital for security and stability. Strong audit compliance can be achieved due to the traceability that exists among its requirements, tests, and builds – particularly important in regulated industries. The benefits of using DevOps principles for firmware development include shorter development cycles; quality improvements through hardware validation performed in the development process; improved collaboration between the hardware, firmware, and software development teams; and decreased risk related to deployment due to quick rollback capabilities. Challenges still exist, however: hardware variability must be managed, the firmware pipeline must be protected from bad actors, and scaling across multiple hardware configurations and platforms must be ensured.

#### IV. REAL-WORLD USE CASE

The Azure Cobalt 100 CPU and Maia 100 AI accelerator are significant projects utilizing custom silicon hardware for Microsoft Azure demonstrating the latest in AI accelerators and cloud data center technology. The Cobalt 100 CPU features 128 Neoverse N2 cores based on ARMv9 architecture, providing approximately 40% more performance than previous generations of ARM. The Cobalt CPU has 12 DDR5 memory channels that provide high bandwidth, making it useful in the cloud native applications used in Microsoft Teams and Azure SQL servers. The Cobalt CPU also represents a strategic transition from traditional x86 architecture to ARM-based systems to help with scale and energy efficiency in data centers. Maia 100 AI accelerator is based on 105 billion transistors built using TSMC's 5nm technology and built designed for AI workloads like training large language models. It has a single internal network bandwidth of 4.8 Tbps per chip using integrated RDMA ethernet IO, and was also built to do so with liquid cooling racks to help with energy efficiency, too. However, there is limits with memory bandwidth usage that limit some conclusions based on language models.

The Maia 100 system is being developed to serve as an alternative choice to other competitive AI accelerators like Google TPUv5 and Nvidia H100, incorporating several lessons from Microsoft internal AI services and OpenAI. Microsoft proceeds through the usual process of firmware integration testing and hardware validation of both chips to provide performance and reliability for cloud workloads. This includes joint hardware-firmware validation, power and thermal testing in its own specialized rack designs, and delivery as an integrated solution to Azure's global cloud service. This work manifests Microsoft's focus on distinguishing its cloud platform further with the acquisition of key semiconductor IP and custom engineering solutions for AI and data workloads [16].

Microsoft's Azure Cobalt 100 and Maia 100 chip's hardware validation strategy must also be quite broad, as the chips have specific intended uses as a cloud CPU and an AI accelerator, respectively. The goals of validation are focused on performance, power efficiency, interoperability, and reliability of the chips, specifically their AI capabilities for Maia and ARM components for Cobalt. Thermal performance is likely to be very important for the Maia chip, and will require high-density liquid cooling solutions. To achieve a test environment, hardware-in-the-loop testing, simulation and emulation approaches should be used, coupled with validation facilities which can match Azure's datacenter conditions and physical footprint; including special cooling equipment and Maia racks. Evaluating and vetting firmware and software combination could be completed quickly utilizing FPGA simulators.

Performance testing should evaluate the Cobalt memory subsystem, cache coherency, multithreading, and CPU commands, while the AI capabilities of Maia should be validated using tensor operations, RDMA networking, and model training workloads. Stress testing will be performed to push the chips to extremes in order to identify weaknesses. Firmware and software integration is critical, requiring collaboration to verify the functionality of bootloaders, device drivers, control firmware, and to test AI model deployment frameworks. Security validation will include side channel attack prevention, as well as compliance with legal and data center security standards. After the

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

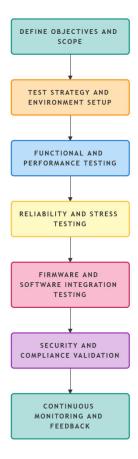

deployment phase is complete, we will continue to test and validate the product in the field by regularly monitoring telemetry and logging, and use that information to improve our designs in the future with input from our Azure service teams, as shown in the below Figure 1:

Figure 1: Step-by-Step Hardware Validation Plan

Effective hardware and firmware processes improve the reliability, security, and performance of cloud services, which all have a direct impact on uptime and, consequently, customer satisfaction. In datacenters like Azure, conducting additional hardware validation, quality assurance of firmware reduces likelihood of errors and outages which reduces unscheduled downtime. Consistent performance under different loads is made possible with hardware-firmware integration, which allows for SLAs (service level agreements) to be met while keeping users satisfied. Upgrades to firmware in a proactive manner along with automatic monitoring decreases incident response times to prevent outages from being prolonged. These enhancements and initiatives lead to improved customer satisfaction through increased service availability; customers are more assured of our cloud services. Purpose-built hardware, such as Azure Cobalt and Maia processors, provides us with optimized performance that enhances the user experience by lowering latency and improving application responsiveness and performance. We improve overall security and policy compliance by implementing the latest firmware updates, as well as secure hardware processes to protect our customers' data against security threats. This infrastructure also offers superior support to businesses adopting cloud native services and advanced AI capabilities for business scalability.

Agile approaches are integrated into hardware/firmware development life-cycle management to improve quality and responsiveness in complex cloud infrastructure deployments such as Azure Cobalt and Maia. Key components of agile approaches are principles such as iterative development, focused engagement with stakeholders, and rapid evaluate-iterate cycles. The key agile elements include reiterative sprints of work in which teams produce intermediate deliverable for stakeholders to check, a backlog of work that is frequently revisited, as agile approaches prioritize revisiting the backlog to manage shifting priorities or requirements, and multidisciplinary teams approaching a problem

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

such as hardware engineers, firmware developers, QA, or operations work, QA concerns need to understand tensions in hardware and firmware goals to discover or ideate on get it can be modific they encounter issues before they are embedded in the development timeline.

Another dimension of agile approaches in complex cloud infrastructure is sensor simulation, a technique that accelerates development because it allows engineers or developers to connect to a device/system without having to simultaneously run on a physical device. This allows developers of firmware to interact and validate their logic without limits to connect to sensor data. Virtual prototyping also helps to make rapid improvements as engineers work through problems iteratively as digital twins, at times, through 3D CAD models to work through design issues in simulation instead of physical Trying to again. Automated regression, on a common testing foundation, testing ensures stability after iterations, enough for DevOps CI/CD. Final, emphasis around reliability and/or fault tolerance is emphasized in every phase of validation, engineering groups strongly validating residual reliability requirements for Cobalt or Maia as part of validation, stress testing, or environmental testing. Tensions comparative to fail too in devices systems of hardware and firmware to pressure tests in tropical testing. Idle monitoring tools support re-coding issues post-launch and additive to validation improvements [17].

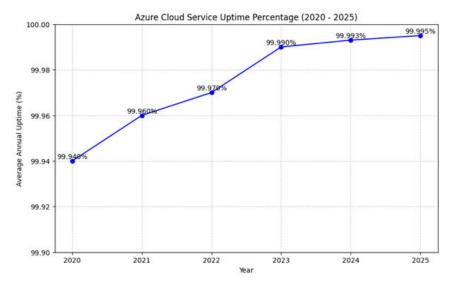

Figure 2:

The statistics shown in the above Figure 2 demonstrate that uptime will gradually improve as hardware and software become better integrated and AGILE and DevOps practices are adopted along with custom silicon tech, such as Cobalt and Maia accelerators. To illustrate this development, the time-series line graph will demonstrate Azure service uptime from 2020 to 2025, with the addition of notations based on infrastructure. The time series will show an analysis of the effect of automation and DevOps integration that can continue to reduce downtime based on incident response time. I will show that continuous firmware updates improve infrastructure available, with minimal impact to users. Working together, the hardware, firmware, and cloud operations teams will resolve issues quickly, resulting in a better customer experience.

#### V. CONCLUSION

The integration of hardware and firmware engineering is increasingly important for the next-generation cloud infrastructure to provide seamless levels of performance, reliability, and faster innovation, particularly as the complexity of cloud workloads continues to rise and we embrace new AI-driven needs in the clouds. There is a need to collaborate closely within teams to bridge hardware and firmware to satisfy software needs with minimal integration effort while providing improvements in areas like fault tolerance, power management, and thermal management trying to extend service availability through integration improvement. Future directions will include the use of AI-driven test automation to improve the validation process, and virtualization and digital twins for testing earlier in the deployment

| e-ISSN: 2320-9801, p-ISSN: 2320-9798| Impact Factor: 8.771| ESTD Year: 2013|

### International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

lifecycle workstream, along with the use of DevOps and Agile for improved continuous lifecycle improvements, and improved heterogeneous computing architectures for various processing units managed by the integrated firmware stack, and improved automation of security and compliance mechanisms to improve overall workflows. It is important to note that working closely between hardware and firmware engineering will be important to provide reliable, scalable, and secure technical cloud services to improve the overall user experience while minimizing service outages on the platform.

#### REFERENCES

- 1. "What is cloud infrastructure?", Scott Robinson, James Montgomery, Kurt Marko, Oct 02, 2024, <a href="https://www.techtarget.com/searchcloudcomputing/definition/cloud-infrastructure">https://www.techtarget.com/searchcloudcomputing/definition/cloud-infrastructure</a>.

- 2. "7 Key Benefits of Microservices Architecture for Modern Applications", Chiara Civardi, 27 Feb 2025, <a href="https://payara.fish/blog/benefits-of-microservices-architecture/">https://payara.fish/blog/benefits-of-microservices-architecture/</a>.

- 3. "Why Software, Hardware, and Firmware Collaboration is Critical", February 15, 2022, <a href="https://www.getbild.com/blog/why-software-hardware-and-firmware-collaboration-is-critical">https://www.getbild.com/blog/why-software-hardware-and-firmware-collaboration-is-critical</a>.

- 4. "Hardware and Software Integration: Combat Challenges in Various Approaches", Mahil Jasani, Mar 27, 2025, <a href="https://www.excellentwebworld.com/hardware-software-integration-solutions/">https://www.excellentwebworld.com/hardware-software-integration-solutions/</a>.

- 5. "Securing Firmware Updates: Addressing Security Challenges in UEFI Capsule Update Mechanisms", Younus Ahamad Shaik, Pankaj Yadav, 03.07.2024, <a href="https://ijisae.org/index.php/IJISAE/article/view/6378">https://ijisae.org/index.php/IJISAE/article/view/6378</a>.

- 6. "When Firmware Modifications Attack: A Case Study of Embedded Exploitation", Ang Cui, Michael Costello, Salvatore J. Stolfo, <a href="https://www.ndss-symposium.org/wp-content/uploads/2017/09/03\_4\_0.pdf">https://www.ndss-symposium.org/wp-content/uploads/2017/09/03\_4\_0.pdf</a>.

- 7. "The Hardware Lifecycle: Essential Stages for Success", Ignacio Graglia, March 5, 2025, <a href="https://blog.invgate.com/hardware-lifecycle">https://blog.invgate.com/hardware-lifecycle</a>.

- 8. "Stage-Gate Process in Project Management: A Quick Guide", Alyssa Scavetta, Dec 13, 2024, <a href="https://www.projectmanager.com/blog/phase-gate-process">https://www.projectmanager.com/blog/phase-gate-process</a>.

- 9. "Automated Testing Techniques for Embedded Software Systems", Codewave, October 16, 2024, <a href="https://codewave.com/insights/automated-testing-embedded-software-techniques/">https://codewave.com/insights/automated-testing-embedded-software-techniques/</a>.

- 10. "Firmware vs Software vs Hardware: The Power of an All-in-One Development Approach", <a href="https://www.hatch-pd.com/blog/firmware-vs-bardware-the-power-of-an-all-in-one-development-approach">https://www.hatch-pd.com/blog/firmware-vs-bardware-the-power-of-an-all-in-one-development-approach</a>.

- 11. "How to Test and Validate Firmware in Hardware-in-the-Loop (HIL) Environments", Lance Harvie, September 18, 2024, <a href="https://runtimerec.com/how-to-test-and-validate-firmware-in-hardware-in-the-loop-hil-environments/">https://runtimerec.com/how-to-test-and-validate-firmware-in-hardware-in-the-loop-hil-environments/</a>.

- 12. "Data Center Accelerator Market", <a href="https://www.factmr.com/report/data-center-accelerator-market">https://www.factmr.com/report/data-center-accelerator-market</a>.

- 13. "Revolutionizing Data Centers: Opportunities and Challenges in Automation", <a href="https://www.webwerks.in/blogs/revolutionizing-data-centers-opportunities-and-challenges-automation">https://www.webwerks.in/blogs/revolutionizing-data-centers-opportunities-and-challenges-automation</a>.

- 14. "Software and Firmware Updates: The Backbone of Data Center Reliability and Security", Hassan Raza, January 25, 2025, https://www.linkedin.com/pulse/software-firmware-updates-backbone-data-center-reliability-raza-pac3f/.

- 15. "How to Implement a DevOps Pipeline for Firmware CI/CD in Your Firmware", November 19, 2024, <a href="https://www.omi.me/blogs/firmware-features/how-to-implement-a-devops-pipeline-for-firmware-ci-cd-in-your-firmware">https://www.omi.me/blogs/firmware-features/how-to-implement-a-devops-pipeline-for-firmware-ci-cd-in-your-firmware</a>.

- 16. "With a systems approach to chips, Microsoft aims to tailor everything 'from silicon to service' to meet AI demand", Jake Siegel, November 15, 2023, <a href="https://news.microsoft.com/source/features/ai/in-house-chips-silicon-to-service-to-meet-ai-demand/">https://news.microsoft.com/source/features/ai/in-house-chips-silicon-to-service-to-meet-ai-demand/</a>.

- 17. "Firmware Development Lifecycle", 2025/10/27, <a href="https://www.meegle.com/en\_us/topics/">https://www.meegle.com/en\_us/topics/</a> firmware-development-lifecycle.

### INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN COMPUTER & COMMUNICATION ENGINEERING

📵 9940 572 462 🔯 6381 907 438 🔀 ijircce@gmail.com